# High Area Efficient Spanning Tree Based Modified Booth Multiplier Design for Fir Filter Using Cadence

T.Revathi Associate Professor, Department of ECE, Tejaa Shakthi Institute of Technology for Women, Coimbatore, Tamilnadu-641659. Srksuresh@Gmail.Com S. Jayasudha PG Scholar, Department of ECE, Tejaa Shakthi Institute of Technology for Women, Coimbatore, Tamilnadu-641659. Revathireva112@Gmail.Com. Dr.N.J.R.Muniraj Principal, Tejaa Shakthi Institute of Technology for Women, Coimbatore, Tamilnadu-641659. ENjrmuniraj@Yahoo.Co.In

Abstract: Now a day the finite impulse response (FIR) filters are extensively used in various digital signal processing applications. Such as digital audio, data transmission etc... there are several techniques are used to the FIR filter circuit must be capable to operate at high sample rate and must be a low power circuit are operating at moderate sample rates. To design and implement the modified booth multiplier for fast computation with less energy and area consumption.Now we proposed an high area efficient spanning tree based booth multiplier design for FIR filter. These techniques were employed to optimized the excessive area and power consumption for large multiplication using spanning tree based modified booth multiplier in FIR filter design. The design was implemented in cadence technology and its optimized the total area efficient .The spanning tree based modified booth multiplier used to consuming highly area efficient and low power for FIR filter.

**Keywords:-** FIR Filter; Modified Booth Multiplier, Spanning Tree.

## I. INTRODUCTION

The digital filters are very important port of digital signal processing. To the advanced technology with digital filters are most used function in multiplication. The proposed technique to design multipliers are high speed and low power consumption and lesser area to implementation of VLSI technique. To using design of fixed width multipliers with linear compensation function topologies are exhibit better accuracy.The high accuracy fixed width modified booth multipliers for application using to save area,power and increment in speed the modified booth multiplier is used to instead of baughwolley multiplier and also used to speedup the multiplication carry lookahead adder is used as a carry propagate adder.To increase the speed mostly used in larger areas. Therefore, compromise the improve the speed of the circuit for a larger improvement in reduction of space and power. The multiplier based on modified booth algorithm and Wallace addition is one of the fast and low power multiplier. The FIR filter design are based on spanning tree based modified booth multiplier. Area of modified booth Wallace multiplier can further be improved by using a modified booth multiplier is the major constraint which defines the performance of the desired filter usually booth multiplier and modified booth multipliers are used for good performance.

## II. LITERATURE SURVEY

Speculative functional units are arithmetic functional units that operate using a predictor for the carry signal. The carry prediction helps to shorten the critical path of the functional unit; the average case performance of these units is determined by the hit rate of the prediction. The Dism is used to optimize the FUS and register binding boost execution time. The data path utilizing both linear structure and logarithmic structure for speculative arithmetic functional unit's So, it's possible to reduce the execution time for logarithmic structure and linear structure [2]. The design of fixed width multipliers with linear compensation functions by investigating in detail with linear compensation function. There are two topologies are used to the fixed width multipliers in Uniform quantization and non-uniform quantization To improving the power and speed and reduce the circuit complexity [3]. The high accuracy fixed width modified booth multipliers for lossy application described on adaptive conditional probability estimator fixed width modified booth multiplier, which can be easily applied to large length booth multiplier for achieving higher accuracy performance. To save the area and power and increment in speed the modified booth multiplier is used to instead of baugh wolley multiplier and also speedup the multiplication. The multipliers are applicable to lossy applications to reduce the area and power consumptions [4].

The fixed width modified booth multiplier using generalized probalistic estimation bias(GPEB) booth multiplier are implemented in the circuit of using 2D-DCT to reduce the area cost. The GPEB booth multiplier can achieve the higher accuracy and most power efficiency. The 2D DCT implementation with the GPEB booth multiplier is achieved by the PSNR and area cost. The GPEB fixed width booth multipliers have low hardware cost and low power consumption while achieving high accuracy [5]. The ACPE is applied to the fixed width booth multiplier is proposed .The ACPE can be easily applied to large length booth multipliers for achieving a higher accuracy performance.

a single compensation formula of ACPE To described adaptive conditional probabilistic estimate applied to fixed width booth multiplier is proposed. To achieving a higher accuracy performance based on the conditional probability theory[6]. The VLSBM (variable latency speculating booth multiplier) is a high speed and energy efficient to perform a speculating and correcting phase. To reduce the critical path and least significant part (LSP) and most significant part (MSP) and an estimation function stochastically predicts the carry to the MSP, thereby allowing Independent calculation of the partial product accumulation of parts.[7].The low cost FIR filter designs by jointly considering the optimization of co-efficient bit width and hardware resources in implementation. To increase the speed and to reduce the complexity of FIR filter, they implemented by using vedic multiplier [8]. The parallel prefix adder are known to have the best performance in VLSI design. This performance advantage does not translate directly into FPGA implementations due to constraints on logic block configuration and routing overhead.

The parallel prefix adders are using to increase the speed and to reduce the power[11]. Parallel prefix adder is the most flexible and widely used for binary addition. Parallel prefix tree is an approach to redesign the basic operator used in parallel prefix architecture. The area requirement can be considered from the utilization of LUTS and slices and overall gate count [12]. The high speed arithmetic in binary computers obtaining high speed in addition, multiplication and division in parallel binary computers are described and then compared with each other as to efficiency of operation and cost [9]. The modified booth multiplier algorithm is an algorithm which multipliers two signed binary numbers in twos complement notation. For designing a lower error and area efficient 2's complement fixed width booth multiplier that receives two n-bit numbers and produces an n-bit product. The unified signed and unsigned multiplier was optimized in terms of speed, power consumption [13].

# III. PROPOSED SYSTEM

The spanning tree based modified booth multiplier module performs the concurrent multiplications of individual delayed

signals and respective filter co efficient, followed by the accumulation of all the products .accumulation is also done by using a modified spanning tree adder is used for previous technique in final addition .A modified spanning tree multiplier is developed here such that it enhances the performance further. To design a low area cost FIR filter with the advantages of reduced power consumption and moderate speed performance. To design and implement the modified booth algorithm and Wallace addition is one of the fast and low power .Multiplier for high speed applications, to furthere improved the booth Wallace multiplier by using a spanning tree based modified booth multiplier. The booth multiplier algorithm or the method of multiplying binary numbers in twos complement notation. Modified booth multiplier is an extension of booth multiplier .Multiplier architecture consists of booth encoder, partial product generator, Wallace tree and a modified spanning tree parallel prefix adder. The modified booth algorithm which encodes the multiplier bits and the partial product generator produces the partial products by operating on multiplicand. This will reduce the number of partial products.

Figure 1 RTL View of Booth Multiplier

#### ISSN No:-2456 -2165

A. Spanning Tree Based Modified Booth Multiplier:

Figure 2 RTL View of Modified Booth Multiplier

The booth multiplier makes use of booth encoding algorithm in order to reduce the number of partial products by processing three at a time during recoding. Tress are an extremely fast structure for summing products.spanning tree based FIR filter consumes less power than that of existing FIR filter.The reduction in number of gates accounted for the reduction in power in spanning tree based FIR filter. The multipliers have the four types of main characteristics in area, accuracy, speed, and speed. The spanning tree to use minimum number of multi input gates and hybrid adder. Therefore proposed FIR filter using modified spanning tree based modified booth multiplier is high area efficient when compared with other two FIR filters.

## IV. SIMULATION AND RESULT

The symmetric form structure of proposed FIR filter is implemented.In this chapter the simulation result of all the circuit has been placed. The FIR filter using spanning tree based modified booth multiplier has been implemented.The booth multiplier and modified booth multiplier coding simulated result in compare the power and area,gates and speed comparison is done using the timing report obtained in the synthesis report. While comparing filters using spanning tree based modified booth multiplier is consuming lesser area .The Xilinx ISE 14.2 software was used to synthesize the design onto the Spartan 3E device.The spanning tree based modified booth multiplier and booth multiplier design has been performed by using the CADENCE tool.The simulation results obtained for the two FIR filters ,namely FIR filter using spanning tree based modified booth multiplier and booth multiplier.

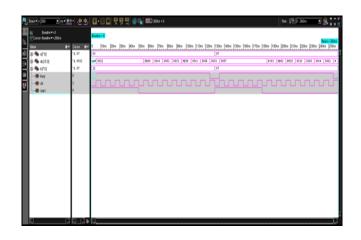

Figure 3 Output Waveform of Fir Filter Based on Booth Multiplier

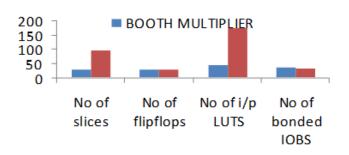

The comparison for the conventional FIR filter using Booth multiplier and modified booth multiplier are shown in a table1.

| FIR filter topology           | Booth multiplier | Modified booth multiplier |

|-------------------------------|------------------|---------------------------|

| No of slices                  | 28               | 96                        |

| No of slice of flip-<br>flops | 28               | 28                        |

| No of I/P LUTS                | 45               | 175                       |

| No of IOBs                    | 35               | 33                        |

## Table 1: Comparison Area of Booth and Modified Booth Multiplier

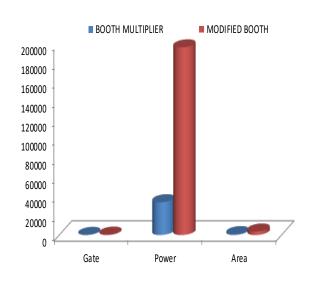

The comparisons for the results are shown in the form of graphical view. When the power reduction will be more in multiplier, while comparing with simple spanning tree based modified booth multiplier power estimation.

| Analysis | Booth multiplier | Modified Booth<br>multiplier |

|----------|------------------|------------------------------|

| Gate     | 95               | 401                          |

| Power    | 34300.811        | 196179.955                   |

| Area     | 984              | 3685                         |

Table 2: Performance Comparison

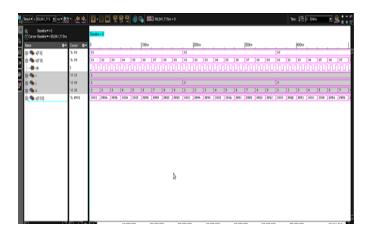

Figure 4 Output Waveform of Fir Filter on Modified Booth Multiplier

Figure 5 Comparison of area in Booth and Modified Booth Multiplier

Now the 8 bit booth multiplier is designed, where the area analysis is compared the spanning tree based modified booth multiplier and booth multiplier it consists of total cell area 401and in modified booth multiplier 984 and for using spanning tree based modified booth multiplier.

Figure 6 Performance Comparison

# V. CONCLUSION

In the design of FIR filter using spanning tree based modified booth multiplier and booth multiplier implementation. A highly area efficient FIR filter using spanning tree based modified booth multiplier is designed based on the symmetric form realization.By employing spanning tree booth multiplier and spanning tree based modified booth multiplier in FIR filter ,area is optimized by 984 and 3685 respectively and power is reduced . The target devices for booth and spanning tree based modified booth multiplier are same in XILINX. Everything has been done in the cadence. This tool it is easy to analysis output of the circuit. For further improvement of high area efficient and power characteristics of multipliers.

## REFERENCES

- [1]. A.DelBarrio and S.O.Memik, M.C.Molina, "A Distributed Controller for managing speculative functional units in high level synthesis", IEEE Trans.comput.AidedDes.Integer.CircuitsSyst.,vol.30,no.3, .pp.350363,March(2011).

- [2]. N.Petra, D.D.Caro, V.Garofalo, "Design of fixed-width multipliers with linear compensation function", IEEE Trans.CircuitsSyst.,vol.58, no.3,pp.350363.May(2011)

- [3]. Jiun-ping wang, Shiann-rong kuang and Shish-chang Liang, "High accuracy fixed width modifiedboothmultipliersfor lossy applications",IEEE Trans.Circuits Syst.,vol.19, no.1,pp.5260. January (2011).

- [4]. Yuan-Ho Chen, T-Y, chang and C-Y.Li, "Area-effective and Power efficient fixed width booth multipliers using generalized probabilistic estimation bias", IEEE Trans.Circuits Syst., vol.1, no.3, pp.277287, September (2011).

- [5]. Yuan-Ho Chen and T-Y Chang , "A High accuracy adaptive conditional –probability estimator for fixed width booth multipliers".IEEE Trans.Circuits Syst.,vol.59,no.3,pp.594-603,March(2012).

- [6]. Shin-kai chen, Chih-wei Liu, "Design and implementation of high speed and energy efficient Variable –latency speculating booth multiplier" (VLSBM), IEEE Trans. Circuits Syst. I, vol.60, no.10, pp.26312643, October(2013).

- [7]. Shen –Fu Hsiao ,Jun-Hong Zhang Jion,and Ming-chihchen, "Low cost FIR filter designs based on faithfully rounded truncated multiple constant multiplication /accumulation",IEEE Trans .Circuits Syst.II, Express Briefs,2013.

- [8]. David H.K.Hoe, chris Martinez and Sri Jyothsna vundavali," Design and characterization of parallel prefix adders Using FPGAS",proc.IEEE,pp.168172,2011.

- [9]. Srinivasamanoj R.M. Sri Hari and B.Ratnaraju, "High speed VLSI implementation of 256 parallel prefix adders", International Journal of Networking Technology, vol.1, no.1, 2012.

- [10]. Shelja Jose, Shereena Mytheen, "Modified booth multiplier based low cast FIR filter Design", International Journal of Engineering Science and Innovative Technology, vol.3, September, 2014.

- [11]. O.L.Macsorley, "High speed arithmetic in binary computers", Proc.IRE, vol.49, pp.67-91, 1961.