# Proposed Topology for 7 Level Inverter: A Comparison

<sup>1</sup>Tanmay Shukla,

B.E. Electrical Engineering From Uec, Ujjain, Currently Pursuing

M.Tech in Power Systems Engineering From Oriental Institute of Science and Technology, Bhopal.

<sup>2</sup>Priyavand Bundela

Associate Professor at Oist, Bhopal.

Abstract:- Inverter, a power electronic device used to convert dc voltage into ac voltage at desired frequency. Being a power electronic device, it is more efficient and reliable due to absence of rotating part. Now a days an inverter is not only a device but also a part of power industry but a simple inverter has only two level so the out coming wave is much distorted form fundamental sine wave which introduces the harmonics into the circuit which makes the total system less efficient along with that the age of system decreases also there is a danger of faulty operation [1]. As the harmonics have heating effect along with distortion which is not good for load as well as whole power system. So the concept of multilevel inverter arises in which the levels of the inverter is increased so that the distortion of the outcoming wave could be minimized [2].as the level rises the sinosoidality of the output wave increases and thus harmonic content decreases.in this paper various standard topologies for multilevel inverters are being studied and a new asymmetrical multilevel inverter topology for 7 level inverter is proposed and its results are being discussed and compared with H-bridge type multilevel inverter.

## I. INTRODUCTION

Multilevel inverter is a further expansion of inverters in which the distortion from the fundamental sine wave is reduced. Now a days in the power industry multilevel inverter found its too much application especially in medium power applications. As they are capable of handling high power and voltages with reduced harmonic distortion [2,3]. Multilevel inverters are the devices in which the voltage across the load is noted and DC voltage source is used to decide the levels. And the circuit in one cycle for different duration is completed in different manner by using different switching arrangements. In this paper a new topology for 7 level inverter is being studied and their results are being compared with conventional symmetrical H-bridge type multilevel inverter.

## II. TOPOLOGIES

Basically, multilevel inverters are of two types first is symmetrical multilevel inverter and asymmetrical multilevel inverter In case of later there can be number of arrangements and in case of former there are three arrangements first is diode clamped multilevel inverter second is flying capacitor type multilevel inverter and third is H-bridge type multilevel inverter. Although they can also be classified according to number of phases which is also done in two i.e. three phase multilevel inverter and single phase multilevel inverter in this paper we are only concerned with single phase multilevel inverter. Basically there are three topologies which are as follows

- Diode clamped multilevel inverter.

- Flying capacitor multilevel inverter.

- H-bridge type multilevel inverter.

#### A. Diode clamped multilevel inverter topology

In diode clamped multilevel inverter topology the diodes are used for clamping and the arrangement in which diodes areused for clampling purpose for a n level inverter n-1 pair of switches are used in this topology. and the switch 1 is connected to[ $\{2(n-1)/2\}+1$ ]thand the second switch is connected through diodes to (n+1) th and so on [6].

## B. Flying capacitor multilevel inverter

In this arrangement the number of switches are equal to the number of switches in diode clamped multilevel inverter arrangement but there is some modification in arrangement that first capacitor is connected to last capacitor then second capacitor connected to second lase capacitor and so on.

The main drawbacks of above two arrangements are the voltage at different level is half of the total voltage at input side which needed to be overcome so, an arrangement of H-bridge type multilevel inverter is being proposed it is also a symmetrical type of arrangement as the voltages used in each and every bridge is of same magnitude [6].

## C. H-bridge type multilevel inverter

In this arrangement the multilevel inverter is prepared by connecting switches in bridge arrangements shown in figure and also each bridge makes capital letter of English alphabet "H" in this arrangement output is of same magnitude as input Dc voltage but it uses more switches unlike other symmetrical topologies [4,6].

## III. 7 LEVEL SYMMETRICAL H-BRIDGE INVERTER

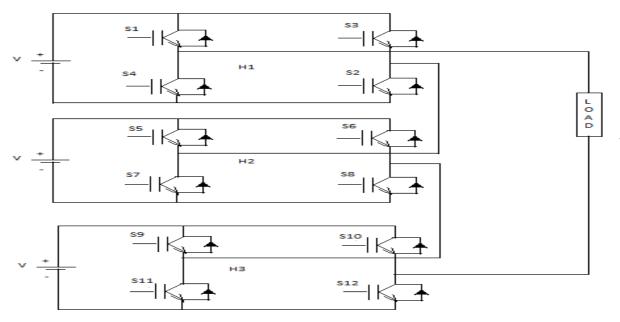

In this symmetrical topology the arrangement of switches is as shown in figure 1 in which 3 bridges are used as in case of seven bridge inverter the voltage at different levels will be +3V, +2V, +1V, 0V, 1V, 2V, 3V in order to approach to level +3V and -3V, three bridges with 1V source each will be used [5,7]. And a proper switching is done in order to get 7

ISSN No:-2456-2165

level output wave. So the total number of switches used in this arrangement is 12 as in one bridge 4 switches are used.

The switching arrangement of different switches in symmetrical 7 level inverter is shown below in table 1.

| Levels  | Switching cycle |    |    |    |     |     |  |  |  |  |

|---------|-----------------|----|----|----|-----|-----|--|--|--|--|

| +3V     | S1              | S2 | S5 | S8 | S9  | S12 |  |  |  |  |

| +2V     | S1              | S2 | S5 | S8 | S11 | S12 |  |  |  |  |

| +1V     | S1              | S2 | S7 | S8 | S11 | S12 |  |  |  |  |

| 0V      | S4              | S2 | S7 | S8 | S11 | S12 |  |  |  |  |

| -1V     | S4              | S3 | S5 | S6 | S9  | S10 |  |  |  |  |

| -2V     | S4              | S3 | S7 | S6 | S9  | S10 |  |  |  |  |

| -3V     | S4              | S3 | S7 | S6 | S11 | S10 |  |  |  |  |

| Table 1 |                 |    |    |    |     |     |  |  |  |  |

#### A. Switching of symmetrical 7 level inverter

Fig 1:- Symmetrical 7 level inverter

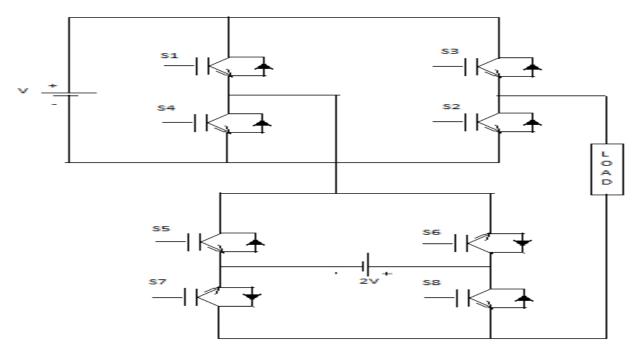

## B. Proposed topology for 7 level inverter

A new a symmetrical topology is being proposed in this paper in which an dc voltage sources are used in which one is used in reverse direction and another is used in forward direction. The one which is used in reverse direction is of twice the magnitude of first. In our new proposed topology for 7 level inverter only 8 switches are used unlike figure 2 the switching arrangement for proposed 7 level inverter is shown in figure. Switching arrangement is shown in Table 2.

| OUTPUT<br>VOLTAGE | S1  | S2  | <b>S</b> 3 | S4  | S5  | <b>S</b> 6 | S7  | <b>S</b> 8 |

|-------------------|-----|-----|------------|-----|-----|------------|-----|------------|

| +3                | OFF | OFF | ON         | ON  | OFF | ON         | ON  | OFF        |

| +2                | OFF | ON  | OFF        | ON  | OFF | ON         | ON  | OFF        |

| +1                | OFF | OFF | ON         | ON  | ON  | OFF        | ON  | OFF        |

| +0                | OFF | ON  | OFF        | ON  | ON  | OFF        | ON  | OFF        |

| -1                | OFF | OFF | ON         | ON  | ON  | OFF        | OFF | ON         |

| -2                | OFF | ON  | OFF        | ON  | ON  | OFF        | OFF | ON         |

| -3                | ON  | ON  | OFF        | OFF | ON  | OFF        | OFF | ON         |

Table 2. Switching of proposed 7 level inverter

Fig 2:- Proposed 7 level inverter

## IV. SIMULATION

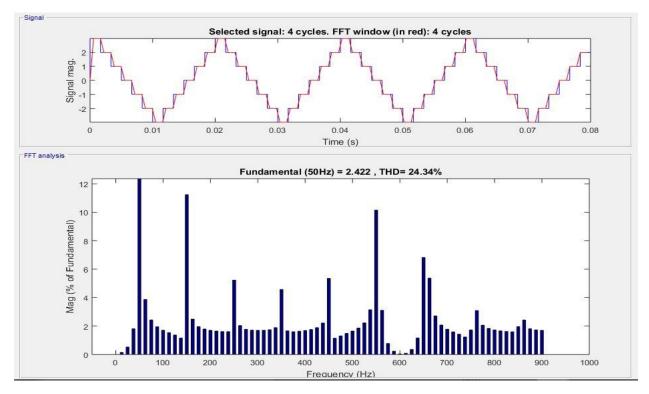

The output wave form of 7 level inverter along with total harmonic distortion for symmetrical H-bridge multilevel inverter is shown in figure 3.

Fig 3:- Simulation of symmetrical 7 level inverter.

#### ISSN No:-2456-2165

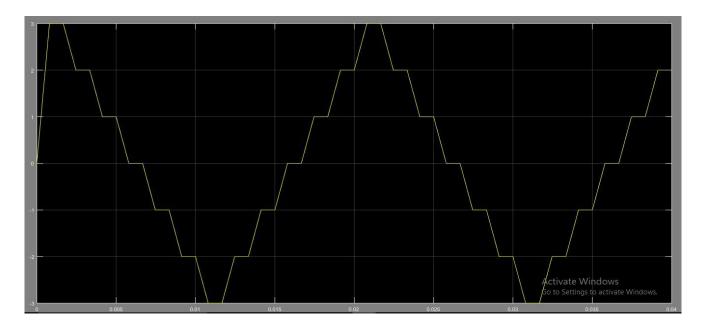

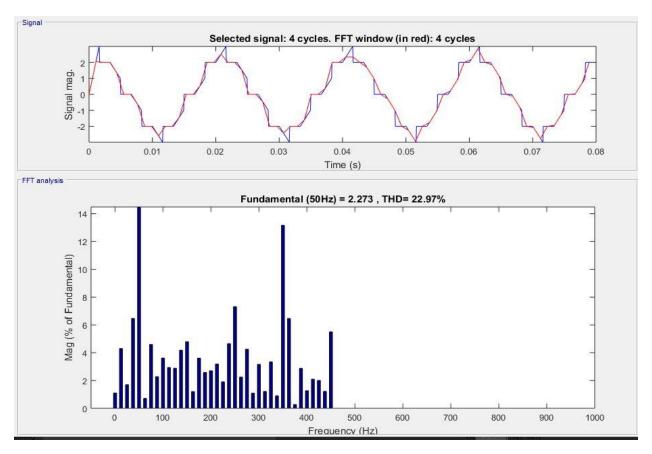

The output wave form of 7 level inverter along with total harmonic distortion for asymmetrical proposed multilevel inverter is shown in figure 4.

Fig 4:- Simulation of proposed multilevel inverter.

## V. CONCLUSION

The number of switches in asymmetrical 7 level multilevel inverter are 8 whereas in case of symmetrical multilevel inverter 12 also only 2 DC sources are used rather than 3 DC sources as in case of 7 level multilevel inverter . Also total harmonic distortion also reduces.

#### REFERENCES

- Y. Suresh anup kumar panda "investigation on hybrid cascaded multilevel inverter with reduced dc sources" renewable and sustainable energy reviews 26 (2013) 49– 59.

- [2]. J. Rodriguez, j. S. Lai and f. Z. Peng, "multilevel inverters: survey of topologies, controls, and applications," ieee transactions on industry applications, vol. 49, no. 4, aug. 2002, pp. 724-738.

- [3]. J. S. Lai and f. Z. Peng, "multilevel converters-a new breed of power converters," ieee trans. Ind. Applications.,vol.32,pp. 509-517, may/june 1996.

- [4]. Gupta, k.k.; jain, s.; , "topology for multilevel inverters to attain maximum number of levels from given dc sources," power electronics, iet , vol.5, no.4, pp.435-446, april 2012.

- [5]. Hema latha javvaji, b. Basavaraja "simulation & analysis of different parameters of various levels of cascaded h bridge multilevel inverter" 2013 ieee asia pacific conference on postgraduate research in microelectronics and electronics (primeasia).

- [6]. Anjali krishna r , l padma suresh , "a brief review on multi level inverter topologies,"2016 international conference on circuit, power and computing technologies [iccpct].

- [7]. Kalpani thantirige, akshay kumar rathore, sanjib kumar panda, suvajit mukherjee, michael a. Zagrodnik, amit kumar gupta, "an open-switch fault detection method for cascaded h-bridge multilevel inverter fed industrial drives,"2016 ieee conference.